Чем в основном занимается разработчик физического уровня интегральных микросхем asic

Bitcoin: история развития, ASIC

Предыдущая часть.

В этот раз рассмотрим заключительную часть истории развития вычислительных систем, предназначенных для добычи биткоинов, а именно эпоху ASIC, поставившую крест на GPU и FPGA майнерах.

Butterfly Labs (BFL)

Но тут ВНЕЗАПНО. Первоначально BFL планировала начать поставки майнеров в начале ноября. Однако сроки многократно сдвигались из-за задержек связанных с производством на фабрике, сборкой и проблемами самой BFL. Также, энергопотребление на уровне 0.8W на GH/s за месяц до появления внезапно подскочило до 1.2W, а корпус сменился с QFN на BGA.

Энергоэффективность микросхем в итоге стала их основной проблемой. Энергопотребление оказалось в 4-8 раз выше планируемого, что вынудило снизить тактовую частоту вдвое с 500MHz до 250MHz. Из-за этого также пришлось вносить изменения во всё оборудование, которое проектировалось под эти чипы. Например, майнер Jalapenos изначально должен был использовать единственный ASIC чип, но, для достижения заявленной производительности в 4.5GH/s, потребовалось использование двух чипов. А итоговое энергопотребление составило

6W на 1GH/s.

А еще оказалось, что только у 60% функционируют все 16 конвейеров, еще у 20% — 15 конвейеров, у 15% — 14, а оставшиеся 5% могут похвастаться лишь 12-13 работающими конвейерами.

Страсти в интернетах

Совершенно ожидаемо, что, в свете этих событий, на интернет-форумах развернулась нешуточная драма. Заказчики, которые профинансировали компанию миллионами долларов, требовали объяснений задержкам поставок. Разнообразные срывы сроков и уточнение спецификаций привели к тому, что клиенты получили первые образцы оборудования только в апреле 2013го. На пять месяцев позже запланированных сроков и почти год после момента фактической оплаты. Огромная задержка поставок существовала до августа 2013.

Клиенты BFL небезосновательно считали, что их покупки стремительно устаревают, даже еще до того, как они успели получить их в руки. Однако изначальные прогнозы относительно сроков разработки, изготовления и масштабных поставок были весьма оптимистичными с самого начала. Особенно, если учесть, что это первый ASIC продукт для BFL. Фактические сроки оказались вполне типичными для данной индустрии, ведь, например, у Intel уходит около года с появления первых тестовых образцов и до начала поставок.

А вот что совсем нетипично, так это уровень прозрачности, который обеспечивала BFL для своих клиентов на протяжении этого времени. Возможно, это объясняется моделью финансирования, основанной на предзаказах. С другой стороны это привело к росту раздражения и злобы среди клиентов, с тревогой следящих за графиком сложности майнинга BTC и гадающих, не поставили ли они не на ту лошадку…

ASICMINER

Деятельность этой компании началась в июле, после того как BFL начала принимать предзаказы на свои майнеры. Компания была основана тремя гражданами Китая и одной из их мотиваций было создать конкуренцию для BFL и не дать той стать единственным поставщиком майнеров. Подход ASICMINER к ведению дел сильно отличался от использованного BFL, поскольку они не располагали тем доверием, что заработала последняя на поставках FPGA-майнеров.

Также примечательно, что сбор средств был проведен исключительно через интернет форумы. Основатели подробно излагали свои планы по разработке ASIC и отвечали на сотни вопросов от онлайн сообщества, многие из которых касались глубоко технических деталей их бизнес модели технических решений и финансовой благонадежности.

В начале августа, когда была завершена первая итерация проектирования, размещения и трассировки, компании удалось привлечь средства через IPO, проведенное на онлайн-бирже GLBSE, осуществлявшей торги в bitcoin. Было предложено продавать 1 из 400 тыс. акций компании за 0.1 BTC, при этом акционерам отходило не более 200 тыс. акций. Бизнес план предполагал начать майнинг на своём собственном оборудовании с общей производительностью 12TH/s, а затем начать прямые продажи чипов или оборудования покупателям. Прибыль должна была распределяться между акционерами, пропорционально их доле в компании.

6го октября биржа GLBSE закрылась из-за взлома и разногласий среди её основателей. Поскольку информация об акционерах хранилась биржей анонимно, представители ASICMINER больше не знали кто их акционеры. Ситуацию усугубил и тот факт, что часть средств, привлеченных в ходе IPO, застряла на счетах биржи. Со временем, на основе электронной почты и других документов, удалось восстановить владельцев примерно 150 тыс. акций. На это ушло два месяца.

К 14 октября был запущен процесс производства и к 31 октября первые вафли добрались до стадии металлизации, за которой следует разрезание вафли на отдельные чипы. Однако фабрика задержала производство, в интересах других, более крупных заказов, и первые готовые чипы появились только 28 декабря.

USB-хаб с целым массивом Block Erupter’ов, каждый из которых дает 330 MH/s или примерно половину производительности GPU AMD 7970. (источник)

Avalon

Bitcoin Hardware Scaling

1.4x на каждый шаг техпроцесса. Логика биткоин-майнера представляет собой едва ли не худший для тёмного кремния случай, еще более худший чем Multicore или GPU, по причине практически полного отсутствия накристальной памяти и высокой активности всех элементов схемы. Т.е. если, допустим, прогресс остановится на 10нм, то можно ожидать лишь

6.5х улучшения производительности, по сравнению с 65нм чипами. История когда BFL пришлось снижать частоту своих чипов из-за ограничений энергопотребления лишь еще раз показывает к чему сейчас приводят попытки вылезти за рамки «дозволенного» тёмным кремнием.

После того, как стремительная смена поколений майнеров перешла к переходу на ASIC, разница между последующими поколениями майнеров будет не настолько велика, чтобы быстро отправить на пенсию старое железо. Полная аналогия с ПК – если в середине 90х рост производительности превращал топовое железо в хлам за 2-3года, то сейчас и 5-летнее железо выглядит очень даже неплохо. Для производителей ASIC это будет означать погоню за энергоэффективностью, а не производительностью. А среди групп энтузиастов майнинга наибольшую выгоду получит тот, у кого будет доступ к наиболее дешевой электроэнергии. Уже сейчас известны случаи, когда скупалось старое оборудование для майнинга и возвращалось в строй, скажем, вблизи электростанций, где тарифы на электроэнергию намного ниже городских.

Оптимизация энергоэффективности

5.5W на GH/s. Для 130нм-ASICMINER и 110нм-Avalon чипов эти цифры составляют 8W и 9W соответственно. Согласно закону Деннарда, при переходе на 14нм можно ожидать 65/14 = 4.6x снижение энергопотребления, примерно до уровня 1W на GH/s.

Правда, т.к. первые поколения ASIC-майнеров ставили своей целью перейти от FPGA в эпоху ASIC, то, вероятно, есть огромный простор для дальнейших оптимизаций архитектуры и схемотехники с целью сократить энергопотребление, не ухудшив производительность и не увеличивая площадь. Среди таких оптимизаций может оказаться использование нескольких уровней напряжения, замена триггеров на latches или даже использование самосинхронной схемотехники, чтобы сэкономить энергию, которая тратится на тактирование. Согласно экспертным оценкам, есть еще по крайней мере четырехкратная возможность снижения энергопотребления в рамках используемого техпроцесса.

Помимо базовых оптимизаций существует много улучшений, характерных для тёмного кремния, и для которых ASIC-майнер отлично подходит. Например, использование уровней напряжения, близких к порогу срабатывания (NTV – Near Threshold Voltage). Отсутствие статической памяти и необходимости передавать сигналы на большое расстояние внутри чипа позволяет ожидать здесь еще 5х снижения энергопотребления.

Также, поскольку аппаратная реализация SHA256 очень проста, то можно представить специализированный техпроцесс изготовления для майнеров, по аналогии с разными процессами, применяемыми для чипов памяти и логики сегодня.

Вместо заключения

Чипы, производимые на заказ, наиболее конкурентноспособны по сравнению с массовым производством, если проходят «концентрационный тест» — выгода от использования специализированного чипа должна заключаться в нем самом, а не других компонентах системы. В случае биткоина, прибыльность – прямая характеристики чипа. Лишь с несколькими дополнительными факторами, вроде цен на электричество.

Если вычисления обладают высоким параллелизмом, а специализированная реализация гораздо меньше чем эквивалентный ей код для системы общего назначения, то ASIC – хороший выбор для того, чтобы сделать скачок в производительности.

Как ни странно, но исследования, проводимые в университетах, сыграли весьма скромную роль в разработке ASIC-майнеров. Для этого есть объяснение. Во-первых, университетские исследования направлены на новейшие технологии производства, которые из-за своей нестабильности не подходят для быстрого использования. Во-вторых, у университетов есть бесплатный доступ к САПР, стоимостью десятки миллионов долларов, лицензированным только для некоммерческого использования. Это означает, что выпускник университета просто не знает как делать «железо» дешево, не разорившись на лицензиях.

Время выхода на рынок обратно пропорционально новизне используемого техпроцесса. 130нм появится первым, 65нм появится потом. В тех случаях, где использование ASIC действительно дает выигрыш, нет большой разницы в том, какой техпроцесс используется. Зато очень важно время.

Инвестиционный капитал также не сыграл значительной роли. Во многом благодаря распространенному мнению, что «железные» стартапы слишком дороги и занимают слишком много времени. Пользователи смогли сами профинансировать проект, даже не прибегая и к помощи сайтов вроде kickstarter.

Машины для майнинга биткоинов имеют очень сильное и понятное людям объяснение своей ценности – «вы покупаете майнер и он приносит вам много денег». Кроме того, эта идея уже была проверена на предыдущих поколениях майнеров.

Для того, чтобы добиться инноваций в железе, необходимо перепробовать множество новых идей, при малых затратах. Но современная полупроводниковая индустрия отошла от этого направления в сторону дорогих и очень дорогих чипов. В результате «полупроводниковые» стартапы практически не существуют, и практически нет областей, где можно было бы исследовать рискованные инновационные идеи. Не потому что нет идей, а потому, что уж очень дорого. В то же время сокращается спрос на hardware-engineer’ов на рынке труда, а молодые специалисты уходят в софтверные компании за более высокими зарплатами. Что-то с этим надо делать.

Прототипирование ASIC на FPGA

Разработка микросхем дело сложное, дорогое и долгое. И цена любой ошибки крайне велика. После изготовления кристалла патчами и обновлениями уже ничего не исправить. Поэтому к проверке проектируемых схем на этапе разработки подходят особенно скрупулёзно. Для каждого функционального блока пишутся блочные тесты во всех рабочих и не рабочих режимах. После интеграции блока в общую схему проводятся системные тесты, как этот блок работает составе системы. Все тесты постоянно крутятся в регрессионном тестировании. Даже есть неформальный признак более менее приемлемого уровня тестирования – когда объем кода тестов в 10 раз больше объема кода тестируемого блока. Но все эти тесты не дают ощущения, что схема жизнеспособна, так как любое моделирование это поведение схемы на протяжении сотен миллисекунд максимум. А в жизни схема должна отработать сотни тысяч часов. Однажды я искал сбой, когда на 1 Гбайт переданной информации терялись 1 или 2 байта и никакие функциональные тесты эту проблему не обнаруживали. И проявлялась эта ошибка только на FPGA прототипе будущей микросхемы. О том какие прототипы делали мы и что вообще твориться в мире расскажет эта статья.

Прототипирование будущих микросхем на FPGA это единственный способ проверить как работает схема на реальных задачах в более менее реальном масштабе времени. Прототип позволяет отладить софт, получить первоначальные характеристики производительности и многое другое. Современные FPGA обладают достаточно большим объемом ресурсов для этих задачи. Например, вы можете сами на плате с FPGA за 300$ реализовать полноценный компьютер с процессором Intel 8086.

2004 год

К сожалению самого первого прототипа в залежах нашего шкафа со скелетами найти не удалось, но это была небольшая платка на базе Xilinx Spartan3-400 (XC3S400). 400 означает число тысяч эквивалентах вентилей, которые доступны разработчику для создания своей схемы. Цена платки составляла примерно 50$ и позволяла реализовать в ней простой 8-ми битный микроконтроллер со всей памятью и на частоте 40 МГц. Прототипирование заключалось в том, что разработанный микроконтроллер на ней поморгал светодиодом.

2005 год

Специальная плата для прототипа уже разрабатывалась не как эксперимент, а как осмысленный этап проекта. Применялась уже FPGA Xilinx Spartan3-1000. Т.е. нам уже был доступен 1 млн вентилей, и проектируемый микроконтроллер работал на своей макимальной частоте 48 МГц. И именно на этой плате я ловил те самые 2 потерянных байта на гигабайт. Цена платы составляла примерно 200$.

2007 год

Для нового 32-х разрядного микроконтроллера было очевидно, что 1 млн вентилей может и не хватить. По этому была разработана новая плата на базе Xilinx Spartan3-5000, благодаря которой стало доступно уже 5 млн вентилей. Цена платы составила примерно 500$ и на долгое время эта плата стала основной для прототипирования новых разработок. На ее базе проверялись не только микроконтроллеры, но и различные специализированные микросхемы. Проектируемые микроконтроллер в FPGA работал уже на пониженной частоте в 20 МГц, хотя потом в кремнии работали на частотах 100 МГц и даже 150 МГц.

Прототип 32-х битного микроконтроллера:

Прототип видеокарты (к сожалению в жизнь проект так и не пошел, но готовый RTL ждет своего часа):

Прототип 4-х потового Ethernet коммутатор с встроенными приемопередатчиками:

2010 год

При разработке двухъядерного микроконтроллера (32-х битный RISC + 16 битное DSP ядро) мы наконец дошли до уровня, когда 5 млн было уже мало. Но реализация в FPGA различных усеченных конфигураций будущей микросхемы позволила проверить ее функционирование. Например, реализовывали два ядер (RISC+DSP) и с усеченным набором периферии или же одно ядро(RISC), но зато вся периферия.

2012 год

Новый проект потребовал новой платы, так как требуемый объем внутренней памяти для нового 32-х разрядного DSP ядра уже превосходил доступный объем в самой большой FPGA Spartan. Пришлось переходить на более дорогие и сложные ПЛИС. Время проекта было ограничено, и решили найти уже готовое решение. Выбор пал на плату от INREVIUM c самой большой на то время FPGA Xilinx Virtex-6 XC6VLX760.

2013 год

Для нового 32-х битного специализированного микроконтроллера было решено все же попробовать сделать свою плату. Во-первых, разработчики модулей на FPGA должны развиваться и не бояться применять микросхемами, которые дороже их личных автомобилей, а во-вторых у одного из дистрибьюторов завалялись на складе несколько Virtex-6 XC6VLX550Т и он предлагал их с большим дисконтом. FPGA LX550Т это на одну ступень меньше чем LX760 (примерно на 30% меньше вентилей), но зато конечная цена плат с учетом разработки составила всего около 8К$. Таких плат было собрано 6 шт. Раздавать их заказчикам мы не планировали, а организовали для разработчиков доступ к ним через интернет. В плате было реализовано много интересных решений. Например, файлы прошивок грузились на плату как на MassStorage Device в специальную SD карту, и потом уже из нее загружались в FPGA. Всего на карте может быть до 10 различных прошивок, и через специальную программу управления можно выбрать какую из них использовать в данный момент. Так же реализованы различные защиты «от дурака», что бы случайно не спалить дорогую микросхему. Все это позволяет работать с этими платами удалено, безопасно и доверять их даже студентам. Проектируемый МК в FPGA работал на частоте 40 МГц.

Сама плата (прототип специализированного двухъядерного 32-х битного микроконтроллера):

Прототип специализированной микросхемы для датчиков преобразования угол в код:

К сожалению в данной плате есть несколько недостатков: выбраны «дурные» разъемы для подключения дополнительных модулей, но это пол беды, забыли сделать крепежные отверстия возле разъемов, и модули держатся фактически только в разъемах. Так же что бы получить доступ к некоторым элементам управления основной платы приходится фигурно вырезать модули расширения.

Отечественный опыт

А что же другие разработчики заказных микросхем? Например МЦСТ при прототипировании СБИС 1891ВМ6Я (R-1000, четырёхъядерный процессор с 64-битной архитектурой SPARC v.9) использовала специализированную плату с 10 FPGA Altera Stratix II ( 4 х EP2S180 + 5 x EP2S130 + 1 x EP2S90). Общий объем логических вентилей системы можно оценить в 20 млн.

Сейчас одна микросхема EP2S180 стоит около 8К$. Так что стоимость только микросхем FPGA в прототипе превышает 50К$.

Для прототипирования процессора Эльбрус-4C+ потребовалась уже 21 микросхема Altera Stratix IV EP4SE820 и с суммарным объемом в 100 млн. вентилей (хотя сам МЦСТ приводит цифру в 750 млн) и стоимостью около 200К$. При этом рабочая частота прототипа 9 МГц.

Зарубежный опыт

Сейчас специализированные решения для FPGA прототипирования предлагают компании специализирующиеся на разработке средств САПР для микроэлектроники, хотя пригодные для прототипирования модули можно найти и у других компаний. FPGA прототипы есть у Intel и IBM, но их характеристики не афишируются, и становятся известны широкому кругу, только тогда, когда прототип уже моральна устарел.

Cadence предлагает специальную Rapid Prototyping Platform построенную на базе FPGA Altera Stratix-4 EP4SE820. В минимальной конфигурации платформа состоит из двух (c суммарным объемом в 10 млн вентилей), в максимальной из шести FPGA (c объемом до 30 млн вентилей). Цена одной микросхемы EP4SE820 сегодня

Новая система от Cadence носит название Protium и стоится на базе Xilinx Virtex-7 XC7V2000Т и позволяет реализовать от 25 млн на двух FPGA до 100 млн вентилей на восьми. Стоимость одной микросхемы XC7V2000Т сейчас около 20К$. Т.е. в полной комплектации Protium будет стоить не менее 160К$.

Компания Aldec помимо средств разработки так же предлагает платформу для FPGA протоипирования HES-7.

На одной плате расположено до шесть FPGA Xilinx Virtex-7 XC7V2000Т или UltraSacle XCVU440. В случае реализации модуля на базе FPGA UltraSacle XCVU440 суммарное число вентилей достигает 158 млн. С помощью дополнительной платы можно собрать в единый модуль 24 микросхемы FPGA и получить 633 млн вентилей. Стоимость одной микросхемы XCVU440 сейчас 49К$. А максимальная суммарная стоимость всех FPGA переваливает за 1М$.

Synopsys имеет наверное наибольший опыт в разработке платформ для FPGA прототипирвоания. Ранние их модели строились на базе FPGA Virtex-6 (HAPS-60), затем Virtex-7 (HAPS-70). Последняя их разработка HAPS-80 в одном модуле содержит от одной до четырех FPGA Xilinx UltraScale XCVU440.

Готовые модули можно объединять в единую стойку. И в этом случае суммарный объем составляет рекордные 1,6 млрд вентилей.

При использовании одной FPGA максимальная частота до 300 МГц, при использовании соседних в одном модуле до 100 МГц, при использовании нескольких модулей частота снижается до 30 МГц.

Таким образом, имея примерно 3,5М$ на приобретение FPGA вы сможете собрать платформу пригодную для прототипирования Intel Xeon E7. Ну или подождать 20 лет, когда FPGA такого объема подешевеют до пары сотен долларов.

Про ASIC-и, FPGA-сики и ProASIC-и.

Программируемые логические интегральные схемы (ПЛИС) – один из продуктов прогресса микроэлектронной промышленности, применяемый для реализации всевозможных цифровых устройств самой разной сложности. Появились они около 20-ти лет назад и быстро завоевали лидерство в области разработки схемных решений для цифровых устройств. Основные производители ПЛИС: корпорации «Altera», «Xilinx», «Lattice semiconductor», «Actel».

Принципиальная разница между ними в том, что у CPLD базовый слой содержит укрупненные логические блоки на основе элементарных вентилей (2И-НЕ/2ИЛИ-НЕ), а у FPGA этот слой содержит более компактные логические ячейки на основе таблиц истинности (LUT) и количество логических ячеек в базовом слое FPGA превышает количество онных в CPLD на 1-2 порядка. Вследствие этого FPGA имеет более гибкую архитектуру.

Поскольку в элементарной ячейке памяти FLASH-типа используется всего 1 транзистор с плавающим затвором, то размеры ячейки уменьшаются и площадь, занятая такой ячейкой на кристалле, приблизительно в 7 раз меньше площади, занимаемой SRAM-ячейкой. Как следствие этого, снижается суммарный ток потребления кристалла и растет быстродействие таких микросхем. Технология FLASH-ПЛИС позволяет изготавливать микросхемы с рекордно низкими уровнями потребления в статическом режиме. На приведенных рисунках хорошо видны энергетические преимущества FPGA-чипов, изготовленных по FLASH-технологии перед аналогами, выполненными на SRAM-технологии.

Еще одно очень важное преимущество в использовании FLASH-технологии конфигурирования FPGA состоит в том, что в данном случае становится невозможно скопировать битовый поток конфигурационной информации, идущий в момент загрузки конфигурации от внешнего ППЗУ к FPGA. Для защиты интеллектуальной собственности проектов, в случае использования FPGA выполненных по SRAM-технологии, разработчикам приходится прибегать к различным схемно-программным ухищрениям. К примеру: типа установки дополнительных контроллеров или CPLD, шифрующих битовый поток данных либо подключать резервный источник питания для FPGA, обеспечивающий питание конфигурационной памяти в режиме микропотребления.

Эволюция ASIC — что будет с вычислительными устройствами для майнинга

Производители асиков стремятся сделать свои устройства более мощными и энергоэффективными. Они разрабатывают новые чипы и экспериментируют с охлаждением. Узкофункциональные устройства обрастают дополнительными опциями и примочками. Не приведёт ли это к тому, что для новых устройств понадобится ещё больше площадей и электроэнергии? Давайте узнаем, какие перспективы у ASIC на ближайшие два-три года.

Что такое ASIC майнер

Дословно аббревиатура ASIC расшифровывается как application-specific integrated circuit, «интегральная схема специального назначения». Проще говоря, это схема, предназначенная для решения конкретной задачи. Если схему общего назначения можно запрограммировать на выполнение ряда операций, то специализированную — лишь на что-то одно. В некоторых случаях это выгодно и оправданно, ведь однотипные вычисления, на которые направлена вся мощь чипа, происходят быстрее и как следствие дешевле.

Поначалу такие микросхемы (однокристальные системы) использовали для декодирования аудио и видео, в мобильных телефонах и других простых устройствах. Но с развитием майнинговой отрасли стало ясно, что в этой области проходят масштабные однотипные операции в рамках конкретного алгоритма (SHA-256, Scrypt и т. д.). Изначально для распараллеливания вычислений использовали процессорную мощность GPU, а затем перешли на специальные устройства, которые так и назвали — ASIC.

Какие существуют ASIC

Все асики имеют общее устройство. Это небольшая, но увесистая металлическая коробка, с чипами, блоком питания и мощной системой охлаждения. Главные характеристики ASIC – это мощность (хешрейт, Th/s) и потребление электричества. Цена зависит, как правило, от хешрейта, чем он выше, тем больше нужно заплатить за асик.

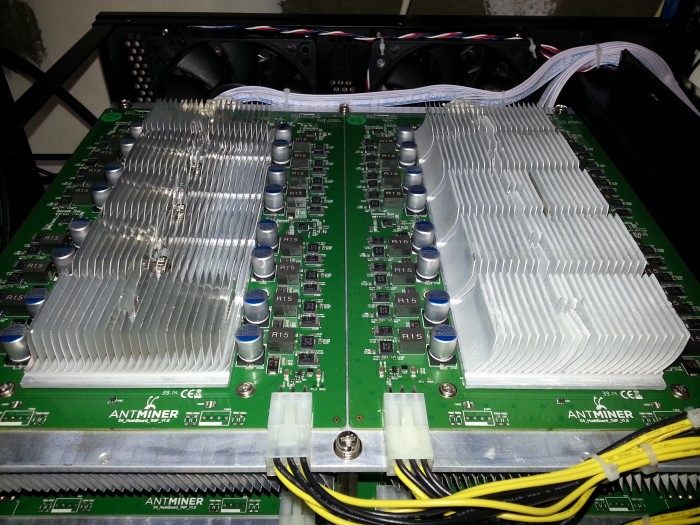

Доминирующее положение (около 75% мирового рынка по состоянию на зиму 2018 года) занимает производитель Bitmain Technologies, поставляющий любое оборудование для майнинга. Оценка его рыночной капитализации приближается к 10-12 млрд долларов. Основатели компании — Джихан Ву и Микри Жан — задумывались о создании специализированных устройств для майнинга ещё в 2013 году. К концу 2017 года прибыль компании составила 2,5 млрд долларов, а чистая прибыль только за первый квартал 2018 года — 1,1 млрд. Производитель обладает брендами Antminer, Antpool и Hashnest.

В мае 2016 года на рынок вышел один из самых популярных и распространенных майнеров для добычи биткоина — S9. В его основе лежит 16-нм микросхема. Средний хешрейт девайса составляет 14,5 Th/s.

С существенным отставанием в доле рынка следует компания Canaan Creative. Она также существует уже около пяти лет и специализируется на блокчейн-серверах и изготовлении микропроцессоров. Выручка за минувший год составила около 200 млн долларов. Основатель компании Ин Джи Йонг, как считается, первым интегрировал чипы исключительно для майнинга в FPGA-устройство (переходную модель между GPU и ASIC) и создал два бренда — Icarus и Lancelot. Затем появился и бренд Avalon.

Среди других производителей, которые предлагают купить майнеры, отметим Ebang. Это тоже китайский вендор, основанный в 2010 году. В майнинг компания пришла лишь в 2016 году, запустив собственную серию майнеров Ebit на техпроцессе 10 нм.

Также в мире известны компании INNOSILICON, CoinTerra, Hashfast, Baikal и т. д.

Wi-Fi роутеры для майнинга

В погоне за расположением и кошельками клиентов производители выпускают новые решения, призванные приносить их обладателям прибыль. Например, в августе 2018 года Bitmain объявил о выходе Wi-Fi роутеров Antrouter R3-DASH и Antrouter R3-SIA, предназначенных для добычи соответственно криптовалюты DASH и Siacoin. За основу этих майнеров взяли корпус для майнинга Bitmain R3.

Вычислительная мощность устройств составляет 300 Mh/s для Dash при потреблении электроэнергии 24,37 Вт и 11,54 Gh/s для Siacoin при потреблении 22,6 Вт. Весят устройства не более 0,6 кг, а цена за единицу составляет около 58 долларов США. Всё, что требуется от пользователей — подключить устройство к Интернету и обеспечить питанием. Устройство начинает майнить, используя Bitmain-аккаунт холдера и по умолчанию подключено к майнинговому пулу Antpool.

Устройства двойного назначения — отличное решение для майнинга и остаётся надеяться, что Bitmain продолжит развитие в данном направлении.

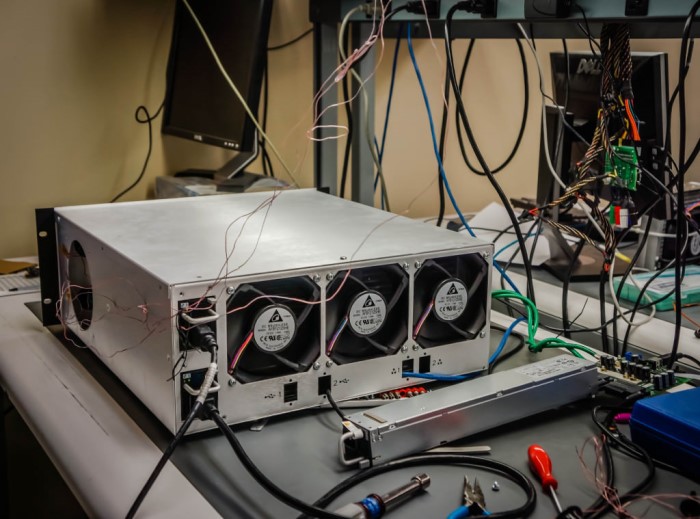

ASIC-фермы с водяным охлаждением

Некоторые производители, например, Cointerra, выпускали каркасы для майнинга, состоящие из ASIC-чипов и упакованные в стандартный корпус для промышленных серверов 4U. Такие установки как TerraMiner IV использовали водяное охлаждение. В них применяли ASIC-чипы Goldstrike I на техпроцессе 28 нм.

Каждый из четырёх чипов выдавал до 500 Gh/s, а общая мощность достигала 2 Th/s. Еще пару лет назад такой хешрейт казался заоблачным и его вполне хватало для добычи биткоина в сутки, однако теперь этого недостаточно.

Подобную установку делали и Hashfast. Они использовали чипы Golden Nonce и водяное охлаждение. Два блока питания Seasonic позволяли чипам выдавать 1,2 Th/s.

Гораздо более интересным примером этого года можно считать стойки для майнинга Bitfury Tardis — сервер для промышленного майнинга биткоина. Данный гигант обладает мощностью 80 Th/s и включает от 5 до 8 хешборд-плат. Это закономерный ответ на рост сложности сети и уменьшение вознаграждения за каждый блок.

Гидромайнеры со встроенным жидкостным охлаждением

В конце августа 2018 года Bitmain сообщил о начале производства тюнингованной версии своего хита Antminer S9, используя специально разработанный майнинг корпус. Новая версия получила название Hydro и является первым в мире асиком со встроенным жидкостным охлаждением.

Водяное охлаждение составляет не единственное преимущество новой модели. Её мощность выше аналога S9j и составляет 18 Th/s. Водяное охлаждение, как ожидается, снизит уровень шума и увеличит срок службы устройства. Его электропотребление останется на уровне 1,7 кВт/час.

Спустя месяц производитель объявил о выпуске 7-нанометрового чипа для ASIC-устройств. Переход на данный техпроцесс увеличит производительность устройств минимум в 2 раза по сравнению с существующим. Это предоставит Bitmain серьёзные конкурентные преимущества и поможет им завоевать еще большую долю рынка.

Воздушное охлаждение для S15 и T15

Параллельно с водяным охлаждением Bitmain анонсировал и вполне привычные устройства на воздушном охлаждении. Это произошло спустя пару месяцев после анонса чипов на базе 7 нм техпроцесса. Они получили наименование S15 и T15 и обещали пользователям прирост производительности при малом потреблении электроэнергии.

В частности, модель S15 выдаёт 28 Th/s при использовании мощности блока питания на 1,6 кВт и 17 Th/s при эконом-режиме на 850 Вт. Устройство T15 на полной мощности выдаёт 23 Th/s (при мощности 1,5 кВт) и 20 Th/s в энергосберегающем режиме на 1,2 кВт.

Выход традиционных моделей после анонса S9 Hydro показывает, что производители пока не готовы целиком «погрузиться» в жидкостное охлаждение. Трудно сказать, чем вызвано такое решение того же Bitmain. Видимо, техпроцессы в основном налажены под воздушное охлаждение, а «гидроасики» являются скорее экспериментальным решением, перспективным и ориентированным на будущее.

Будущее ASIC-майнеров

В конце 2018-начале 2019 года в майнинге основных криптовалют (прежде всего биткоина) будут преобладать следующие тенденции:

усложнение добычи самых прибыльных криптовалют;

невозможность сменить алгоритм и переключиться на более выгодную криптовалюту;

выход устройств с чипами на новом техпроцессе;

сокращение потребления электроэнергии оборудованием для майнинга;

возможность разгона оборудования с официальными заводскими прошивками;

уменьшение награды за каждый добываемый блок.

Помимо этого очевидно, что производители майнингового оборудования собираются и дальше улучшать систему охлаждения устройств. Пока всё сводится к водяному охлаждению с использованием водоблоков и отведению тепла непосредственно от наиболее горячих элементов. Как правило, это одноконтурные системы. Водоблок устанавливают вплотную к чипу или процессору. При нагреве он повышает температуру циркулирующей воды, которую насос отводит к резервуару. Оттуда вода поступает в теплообменник, от него тепло во внешнюю среду отводит вентилятор. Охлажденная в процессе движения вода вновь подаётся в водоблок и забирает тепло у горячего элемента.

Однако некоторые компании экспериментируют с более перспективными технологиями — там, где используется иммерсионная жидкость.

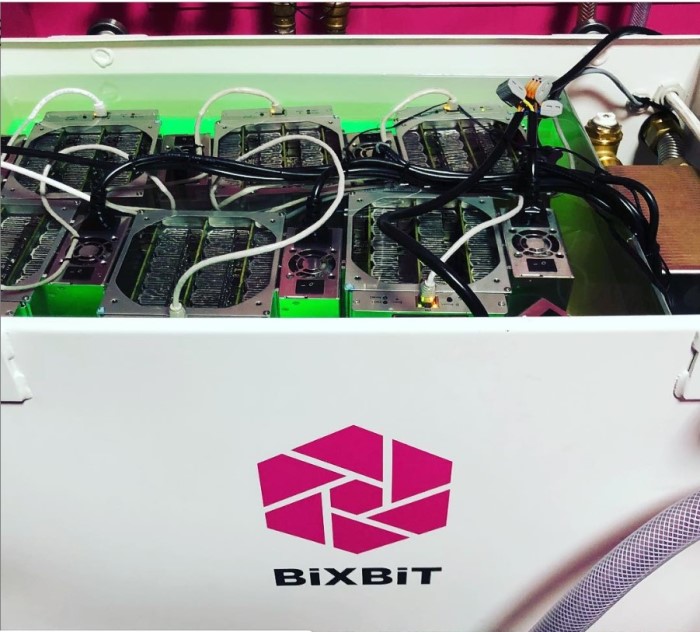

Иммерсионное охлаждение от компании BiXBiT

Иммерсионное охлаждение подразумевает полное погружение работающих устройств, GPU или ASIC, в диэлектрическую жидкость-теплоноситель. Жидкость должна обладать особым набором свойств, препятствующих выходу из строя оборудования и быть совместимой с большинством используемых компонентов. В результате долгих изысканий, методом практических проб и ошибок, компания BiXBiT нашла такой состав, который оптимально подходит для погружения в него любых асиков, как моделей прошлых лет, так и перспективных. Кстати, купить иммерсионную жидкость для майнинга можно отдельно.

Наша ячейка имеет габариты 750х440х380 мм, что позволяет разместить 6 ASIC S9 или 24 GPU. При этом для асиков можно использовать более мощные блоки питания — запас на этот случай предусмотрен конструкцией ячейки. Мощные источники питания позволяют осуществлять разгон (до 40% на базе нашей установки), сохраняя таким образом конкурентоспособность даже старых моделей по сравнению с новыми экземплярами.

Каркас для майнинг фермы предусматривает масштабирование и экономию пространства. Потребитель может начать со стартового комплекта в виде ячейки, а затем «подрасти» до стойки и контейнера. По сравнению с фермами на воздушном охлаждении требуется примерно в два раза меньше площади. Это обеспечит промышленную добычу и подарит приятные бонусы, например, в виде полезного использования выделяемого установкой тепла для отопления, обогрева «теплого пола», выращивания теплолюбивых растений и разведения экзотических животных, сушки горячим воздухом и т. д.

Если вы решите купить стойку для майнинга, вам не потребуется обновлять её каждый раз с выходом нового ASIC. Всё, что нужно для последующего охлаждения — это смена каркаса рига под другие асики. Это позволяет рассчитывать на стабильный доход в разрезе 1-3-5 лет без необходимости новых вложений и даже при сохранении курса на основные криптовалюты на уровне 4-6 тыс. долларов США за единицу. Дополнительная экономия достигается за счет покупки OEM-изделий, то есть без вентиляторов и радиаторов и отсутствия расходов на замену расходных материалов.

Экономия электроэнергии при использовании иммерсионного охлаждения достигает 30%. Особенно это заметно при промышленной добыче и при отказе от кондиционирования, создания коридоров для движения воздушных потоков. Исчезает шум и микровибрации, в целом майнинг превращается в более дружелюбный род занятий с дополнительными преимуществами.

Продажа майнеров также не станет проблемой. ASIC, которые побывали в жидкости, выглядят как новые, они лишены заметных признаков износа и не теряют товарный вид. А это значит, что вы всегда можете реализовать их и приобрести новые устройства, более выгодные, мощные и производительные. Процесс избавления от жидкости, конечно, потребует некоторых вложений, но и оборудование выглядит словно снятое с консервации, без пыли и мусора.

В каком бы направлении не пошло дальнейшее развитие интегральных схем и оборудования для майнинга криптовалют, одной из главных проблем будет их охлаждение. Погружной способ является наиболее перспективным, поскольку позволяет утилизировать избыточное тепло и сэкономить на комплектующих, расходе электроэнергии и обслуживании. Разгон оборудования в этом случае происходит стабильнее и оно может конкурировать с новыми образцами.